Zetta Power

Power is a primary care about in modern semiconductor applications.

Zettabolt is addressing power concerns by providing innovative tools which help analyze and reduce power at all stages of the chip design flow.

WHY LOW POWER?

The Low Power Imperative

🔸 Unyielding demand for increased performance, connectivity, and intelligence across all major technology sectors.

🔸 Energy efficiency is no longer just desirable; it’s a critical requirement for product success and user experience.

AI/ML

- Massive compute

- Power-constrained Inference

5G/6G Communication

- Higher data rates

- Complex processing

Automotive

- ADAS, Infotainment

- Electrification (EVs)

IOT & Wearables

- Billions of devices

- Multi-year battery life

- Ultra-low power states

HPC & Data Center

- Exponential compute demand

- Energy cost

- Cooling limits

Mobile & Consumer

- Rich features

- Always-on demands

- Thermal constraint in thin form factors

WHY US

Zettabolt’s Intelligent Low Power Platform

Comprehensive Solution

- Will my chip fail due to physical power structure errors?

- Will my chip meet its power specification for signoff?

- What’s the estimated power impact of my RTL code?

- How can I maximize power savings at RTL?

Zettabolt’s Low Power Family

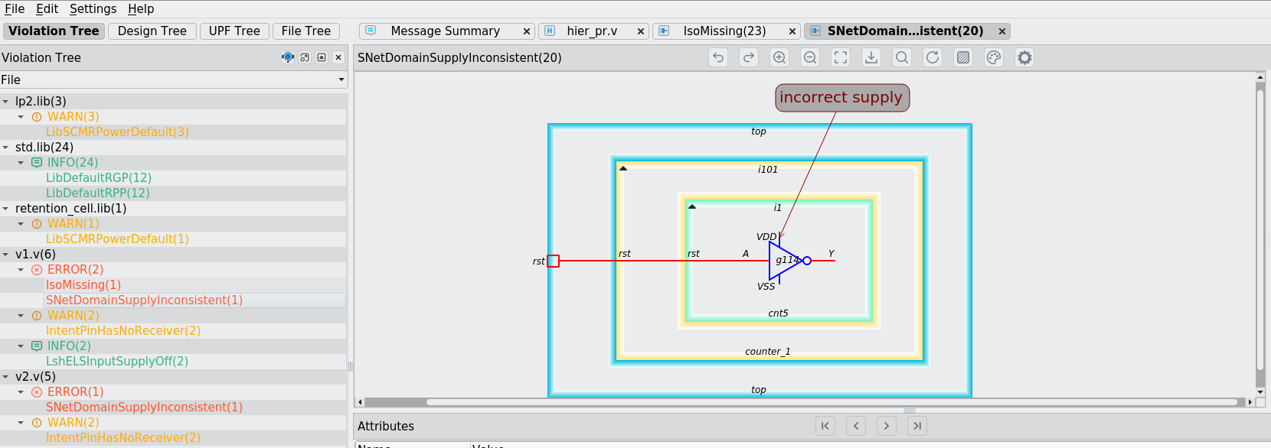

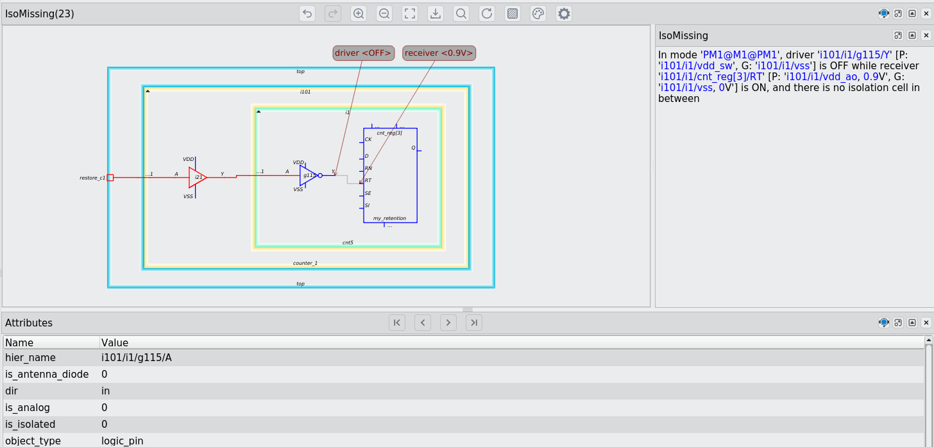

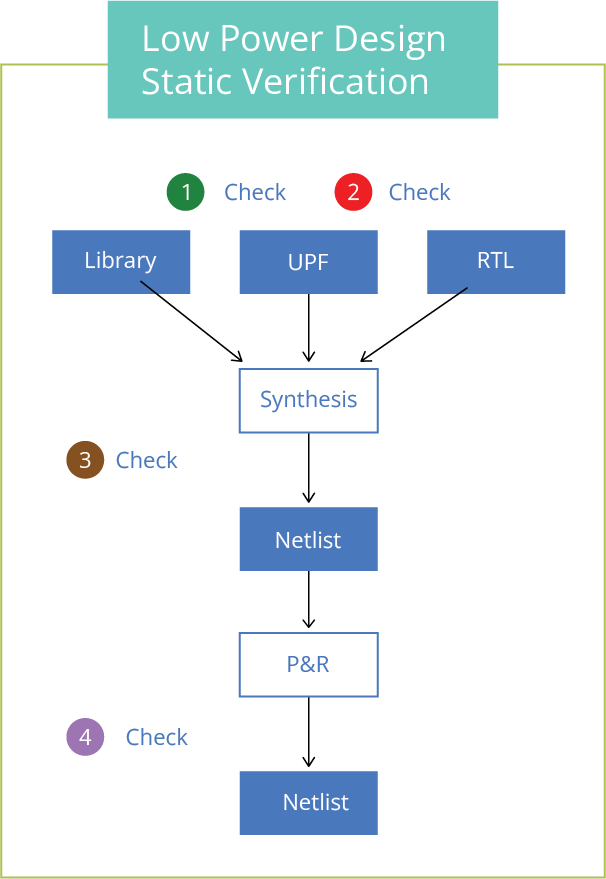

LOW Power Checker (LPC)

1. Library Checks

- Completeness of low power cells

- Correctness of low power cell definitions

- Conflicts with UPF definitions

2. Power Intent Checks

- Missing or redundant low power strategies

- Conflicts in UPF specifications

- Consistency of power states and strategies

3. Logic Netlist Checks

- Missing or redundant low power logic

- Correctness of control signal connection

- Conflicts between UPF and netlist

4. Physical Netlist Checks

- All checks in logic netlist checking

- Correctness of power and ground connections (including substrate)

- Correctness of power switch network

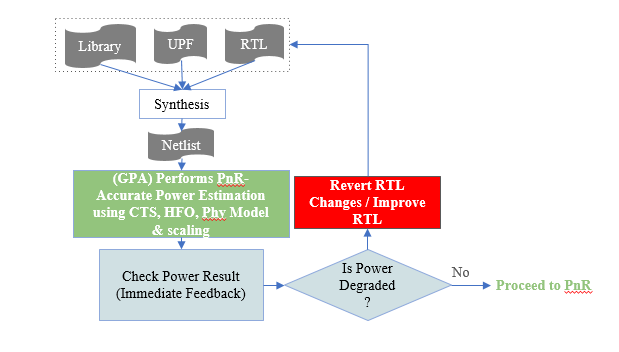

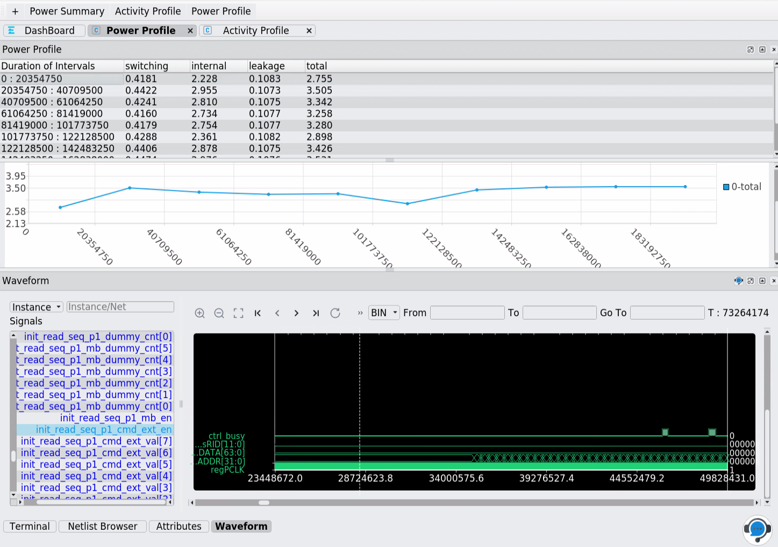

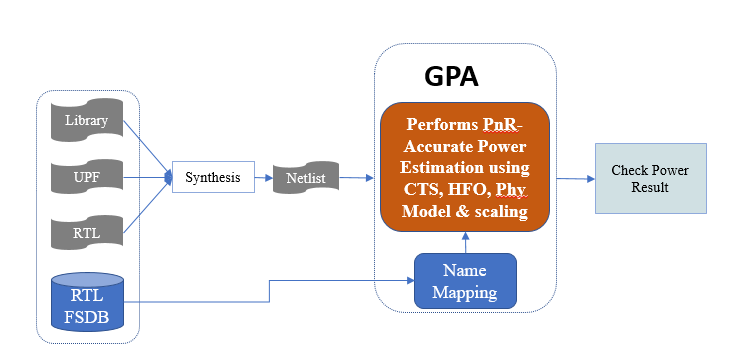

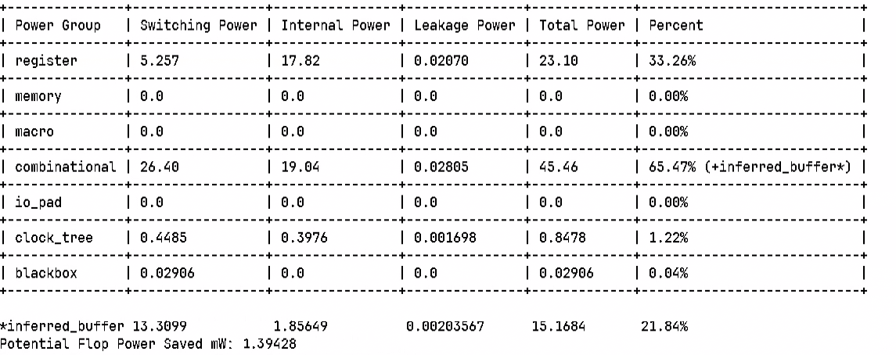

Gate Level Power Analyzer (GPA)

GPA provides the definitive gate-level power analysis and signoff capabilities required for today's most demanding System-on-Chip designs. It is engineered from the ground up to deliver uncompromising accuracy, industry-leading performance, and the capacity needed to ensure confident power closure and accelerate your time-to-market.

Within 2% of sign-off accuracy

Up to 4x faster than other tools

1B+ gate capacity

Support for

- 7nm libraries (with CCS)

- UPF

- SPEF, SDC, SDF

- SAIF / FSDB / VCD

Comprehensive Reports

- Average, Peak, Glitch

- Activity Plots

- Clock-gating efficiency

- Clock-tree

Rich GUI Support

- Design, Schematic viewer

- Power reports

- Activity & Peak-power plots

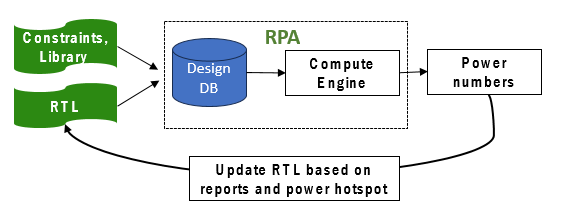

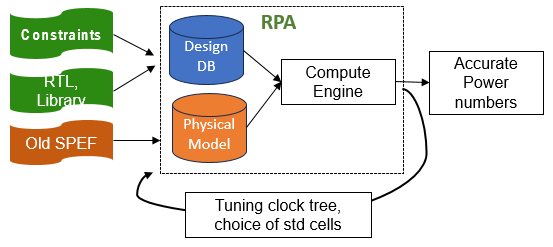

RTL Power Analyzer (RPA)

RPA delivers actionable, early-stage power insights directly at the RTL level, enabling proactive optimizations well before synthesis. Built to integrate seamlessly into your design flow, RPA empowers engineers to make informed, low-risk decisions that reduce overall power consumption.

Within 15% of sign-off accuracy with GPA

10X faster than other RTL synthesis based PA

1B+ gate capacity

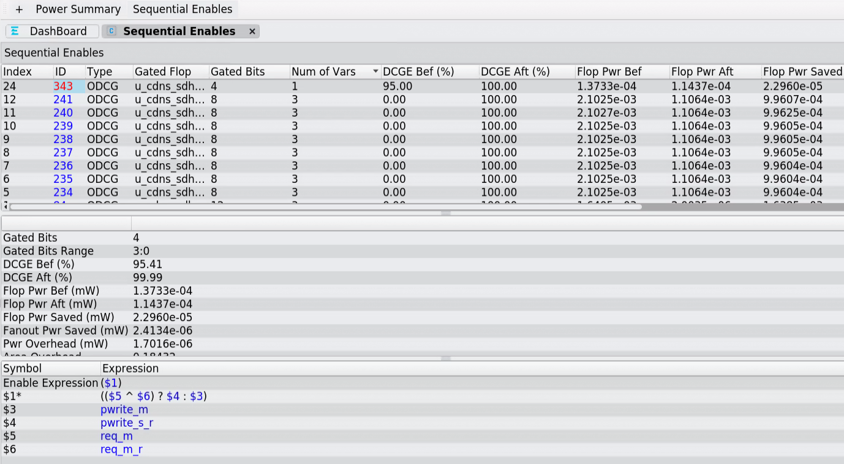

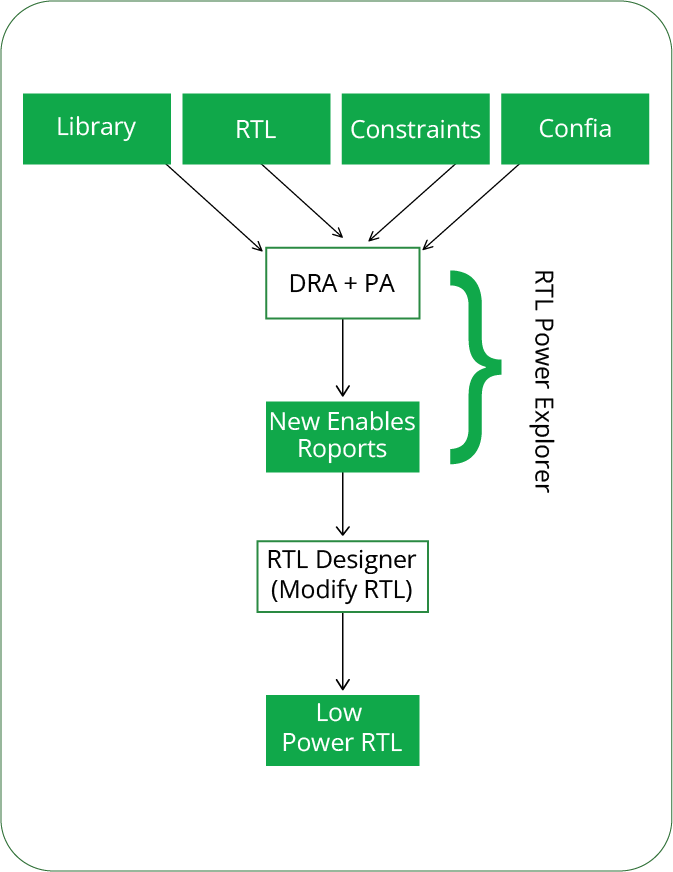

RTL Power Explorer (RPE)

Our advanced RTL Power Exploration (RPE) tool engineered to maximize power savings by identifying and enabling sophisticated clock gating opportunities missed by conventional approaches. RPE dives deep into your design’s sequential behavior to unlock substantial, previously unapproachable power reductions.

Proprietary Deep Reachability Analysis Algorithm

Unique engine performs exhaustive reachability analysis across the flip flop and cone paths to enable clock gating on many logic levels and clock cycles, overcoming the limitations of standard heuristics.

Targeted Exploration & Guidance

Empowers designers by clearly highlighting specific, high-impact gating opportunities and providing actionable insights to guide the implementation of individual changes.

Other Features

• Advanced tools and suggestions for power saving

• Advanced clock trees and reset memory optimizations

• Visualize optimization opportunities

Ready to unlock the full potential of your enterprise knowledge?

OUR CUSTOMER CASE STUDIES