Fast Power Signoff without Full Simulations

Introduction

In modern chip design, time-to-signoff is everything. Our customer was racing to meet a tight tape-out schedule, but a familiar bottleneck kept slowing them down: the gate-level simulation grind.

They had to deliver signoff-quality power numbers, but their flow demanded lengthy, full-design simulations for every mode and corner. The clock was ticking, the simulations were crawling, and valuable engineering cycles were draining away.

Challenge

The problem boiled down to two critical limitations:

- Incomplete Waveforms: They didn’t have the luxury of full VCD/FSDB files for every mode. The only available data was top-level port activity and case-analysis settings for modes like scan and BIST.

- Slow Turnaround: Running multiple, full-chip simulations just to generate power data for different scenarios was painfully slow. Each simulation consumed compute resources and delayed power analysis by days.

The result? Iterations slowed to a crawl, and engineers spent more time waiting on results than actually refining the design.

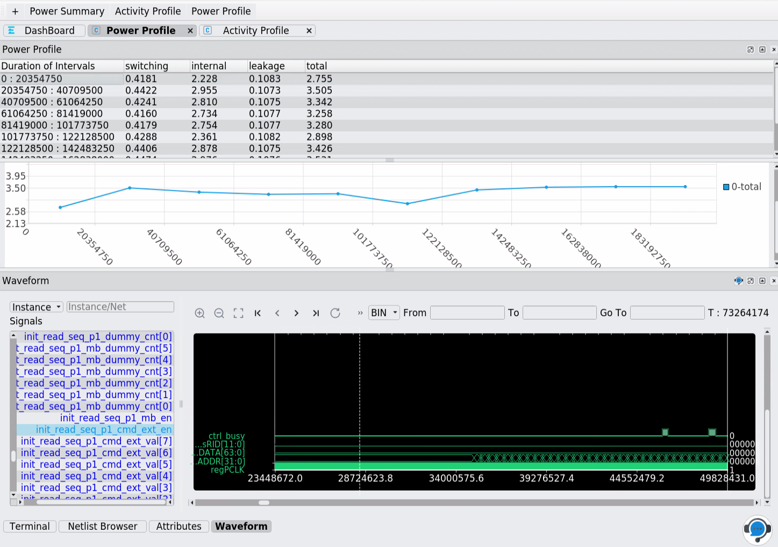

Zettabolt Solution — GPA’s Vectorless Analysis Flow

Enter GPA — Zettabolt’s Gate-level Power Analyzer. Instead of forcing the customer to simulate every detail for every mode, GPA took a smarter route.

- No Full Waveforms Needed: GPA ingested the minimal data they already had — top-level activity numbers plus case-analysis mode settings.

- Intelligent Activity Generation: Using its built-in vectorless simulation engine, GPA propagated realistic switching activity deep into the design hierarchy.

- Rapid Mode Coverage: It could model multiple modes and scenarios without having to run separate full simulations for each.

In essence, GPA replaced days of simulation with hours of intelligent analysis — without compromising on accuracy.

Results

The transformation was dramatic:

- High Accuracy: Power estimates were within 5% of the “golden” full-simulation results.

- Bottleneck Eliminated: No more waiting for full simulations just to run power checks.

- Rapid What-If Analysis: Engineers could now explore a wide range of input activity scenarios quickly, enabling faster decision-making.

- Time Savings: Turnaround time for power analysis dropped from days to just hours.

The customer now uses GPA’s vectorless flow as their standard for early and mid-cycle power signoff, keeping projects on schedule and teams focused on design — not waiting for simulations to finish.