Delivering Universally Optimized IP with RPE

Introduction

For IP providers, power optimization is a unique challenge. Unlike SoC designers, they don’t know exactly how or where their IP will be used.

An IP core might end up in a mobile SoC, a network switch, or a data center accelerator — each with very.

The mission: Deliver “always good” power savings — optimizations that work everywhere, without breaking functionality in any possible integration.

Challenge

Optimizing IP for Unknown Applications

- Diverse Use Cases: The same IP must run efficiently in countless SoC architectures.

- No Specific Stimulus: Customer-specific simulation vectors aren’t available at IP development time.

- Universal Safety: Any optimization must be safe in all contexts — no risky cross-boundary logic or integration-specific gating.

Zettabolt Solution

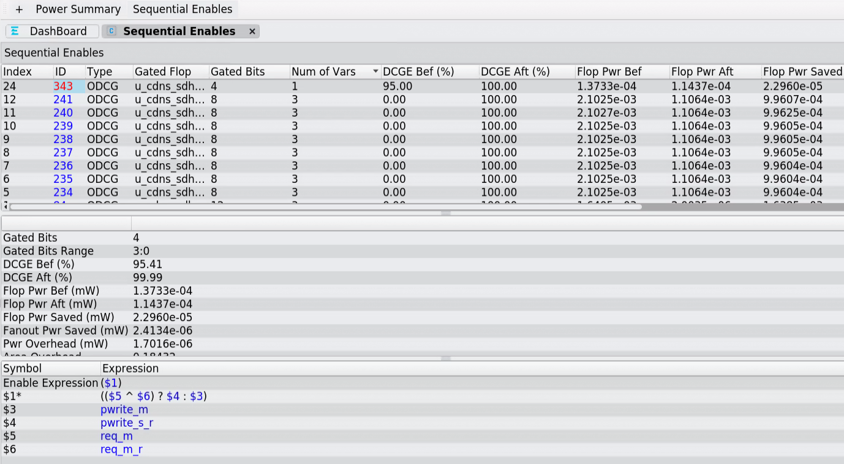

RPE for High-Quality, Localized Gating, The IP provider turned to Zettabolt’s RTL Power Explorer (RPE), configuring it for universal power savings:

- Vectorless Mode: Analysis without requiring stimulus data, ensuring opportunities are not tied to a single use case.

- Localized Optimization: Restricted RPE to clock-gating within each design hierarchy, preventing any optimization that could fail in a different integration.

- High-Impact Simplicity: Focused on finding clean, high-quality enables that are simple to implement and review.

Results

Fast, High-Impact, "Always Good" Savings

The tailored RPE flow delivered exactly what the IP provider needed:

- Runtime: < 2 hours on designs ranging from 5–10 million gates.

- Impact: Found high-quality clock-gating enables for 15% of registers.

- Ease of Adoption: All identified changes were simple to verify and integrate, making them universally safe.

With RPE, the provider shipped a more power-efficient IP core, instantly increasing its value and market appeal across a broad range of customers.