Tackling False Errors in Complex Designs Using LPC

Introduction

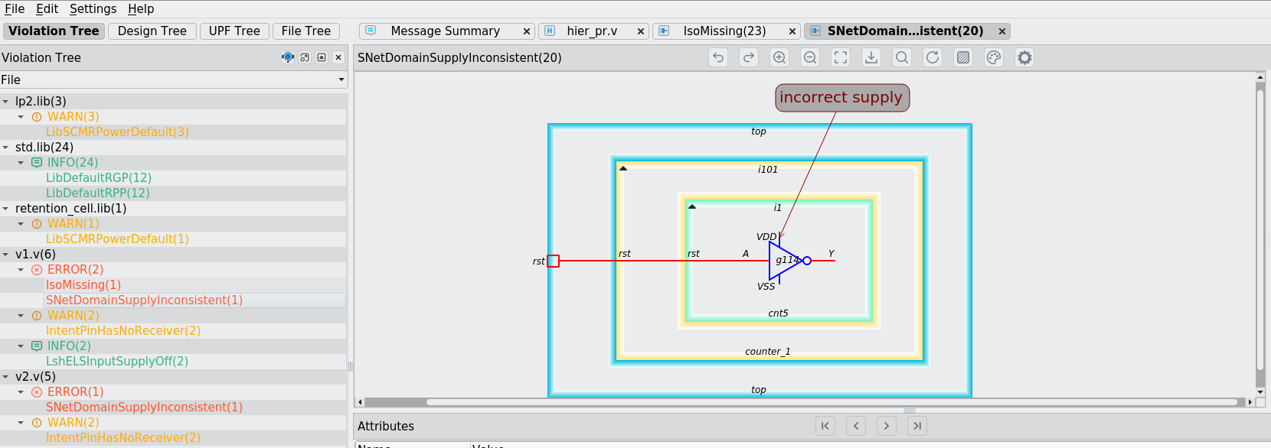

When the Tool Becomes the Trouble : In complex SoC verification, every error reported should matter.But for one customer, their previous low-power verification tool was flooding them with false positives — error messages that looked critical but were actually harmless.

Challenge

Struggle with high number of “false-positive”

- The customer was struggling with a high number of "false positive" errors from their previous low-power verification tool. This was especially problematic in designs with complex power domain relationships and hierarchical UPF files.

- Their engineering team was wasting valuable time debugging issues that were not actual design flaws, leading to significant project delays. One major issue was the incorrect flagging of location violations for isolation cells placed in parent hierarchical instances, a scenario permitted by the UPF LRM.

Zettabolt Solution

LPC’s precise interpretation

- By adopting the LPC tool, the customer was able to significantly reduce the number of false errors. The LPC tool's precise interpretation of the UPF standard, including the handling of isolation cell locations, eliminated the incorrect violation reports they were previously seeing.

Results

- This allowed their engineers to focus on genuine design issues, streamlining the verification process and getting their products to market faster.

Let's Talk