Uncovering Hidden Savings in a Mature Design

Introduction

When You Think There’s Nothing Left to Save, This was a design that had been through it all — years of power optimizations, countless engineering hours, and every clock-gating technique in the book.

The customer’s expert design team was convinced: “We’ve squeezed every last drop of savings out of this chip.” But Zettabolt’s RTL Power Explorer (RPE) had a different story to tell.

Challenge

Is the Design Really Optimized?

- Belief in Perfection: After multiple optimization cycles over several years, the team believed there was no room for further improvement

- Manual, Resource-Heavy Efforts: Previous gains came at the cost of long, painstaking manual work.

- Perceived Plateau: The idea of finding more savings seemed unlikely, if not impossible.

Zettabolt Solution

RPE’s Deep Reachability Analysis: We introduced RPE’s Deep Reachability Analysis — a technique built to uncover what humans (and standard EDA tools) often miss.

- Dual-Run Comparison: RPE was run on both the original and the “fully optimized” versions of the design.

- Advanced Stability & Observability Checks: Its core engine hunted for hidden, hard-to-detect stability and observability conditions.

- Automatic High-Efficiency Clock Gates: Generated clock-gating opportunities that weren’t apparent in manual reviews.

This wasn’t just “running another check” — it was seeing the design through a new lens.

Results

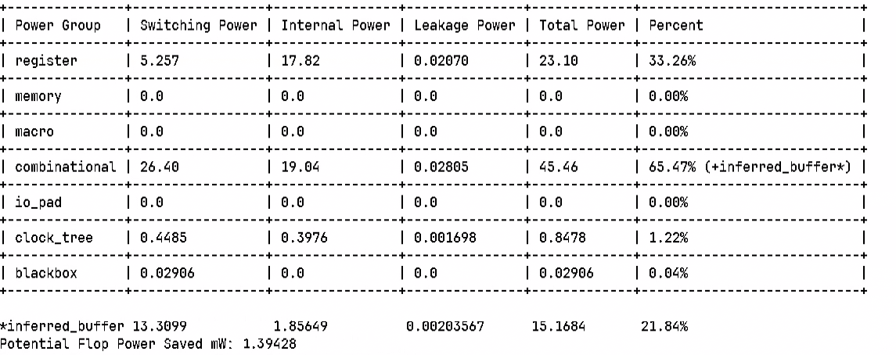

Proven Savings in a “Done” Design, Even on a mature, heavily optimized design, RPE delivered

- 2% Additional Overall Power Savings — after all “obvious” savings had already been taken.

- 5% of Flops Identified with New Clock-Gating Opportunities — these were flops no one thought could be gated.

Customer Testimonial

“Had we tried RPE earlier, it would have saved us years of manual power optimizations!”