Accurate Post-PnR Glitch Power Estimation Using RTL Simulation Data

Introduction

In chip design, what you don’t see can hurt you the most. One of our customers was battling an invisible enemy — glitch power. It wasn’t in the initial reports, it wasn’t in the early power models… but it was very real when the product finally came together.

By the time they detected it, glitch power had already pushed them beyond target budgets, threatening product performance, battery life, and thermal limits. The damage? Weeks of delays, endless rework, and unnecessary engineering stress.

Challenge

The customer’s pain points were clear — and severe:

- Uncontrolled Power Overruns: Glitch power, completely un-modeled in early stages, was a silent contributor that blew past the power targets.

- Blind Spots in Analysis: True glitch detection required gate-level data — but their flow only produced high-level RTL FSDB files.

- Slow Iterations: They had to wait for post-PnR gate-level simulations just to get glitch data, adding weeks to the schedule.

- Inefficient Debug: Even when glitch power was found, localizing the exact sources — down to the nets, cells, and regions — was painfully slow.

This was not just a delay; it was a design-cycle anchor.

Zettabolt Solution

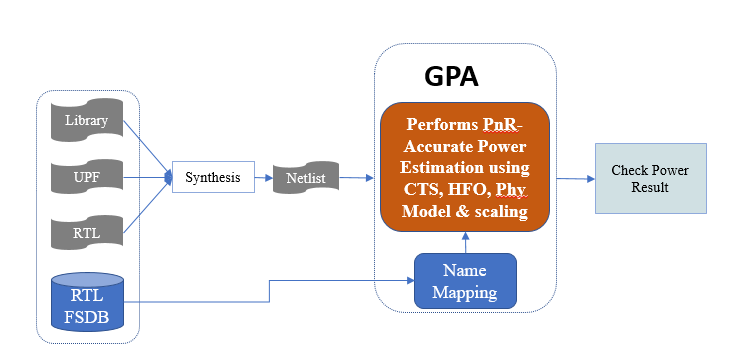

We deployed GPA’s Delay-Aware Glitch Analysis — and the bottleneck was gone.

- Gate-Level Insight from RTL Data: GPA leveraged the existing RTL FSDB and applied it directly to the gate-level netlist — completely avoiding slow gate-level simulations.

- Precision Glitch Detection: Its delay-aware engine accurately propagated timing and activity to identify glitch generation points across the design.

- Actionable Insights: Instead of vague “glitch exists” warnings, GPA delivered targeted reports highlighting exact glitch origins — with coordinates down to regions, cells, and nets.

Results

The customer saw immediate impact:

- Accurate Glitch Localization & Measurement: Glitch sources identified and quantified with high confidence.

- Accelerated Design Cycles: Eliminated the need for costly post-PnR gate-level simulations — saving weeks in the schedule.

- Early Optimization: Engineers could act before glitches compounded into bigger problems.

- Achieved Power Closure: Glitch power was brought under control, and the product met its original specifications

Let's Talk